# LOGIC AND COMPUTER DESIGN FUNDAMENTALS

FIFTH EDITION

GLOBAL EDITION

M. Morris Mano

California State University, Los Angeles

Charles R. Kime

University of Wisconsin, Madison

Tom Martin

Virginia Tech

# **PEARSON**

Boston Columbus Indianapolis New York San Francisco Hoboken Amsterdam Cape Town Dubai London Madrid Milan Munich Paris Montreal Toronto Delhi Mexico City São Paulo Sydney Hong Kong Seoul Singapore Taipei Tokyo Vice President and Editorial Director, ECS: Marcia J. Horton

Executive Editor: Tracy Johnson

Acquisitions Editor: Julie Bai

Assistant Acquisitions Editor, Global Editions: Aditee Agarwal

Executive Marketing Manager: Tim Galligan

Marketing Assistant: Jon Bryant

Senior Managing Editor: Scott Disanno

Production Project Manager: *Greg Dulles*Project Editor, Global Editions: *Donald Villamero*

Program Manager: Joanne Manning

Global HE Director of Vendor Sourcing and

Procurement: Diane Hynes

Pearson Education Limited Edinburgh Gate

Harlow

Essex CM20 2JE

England

and Associated Companies throughout the world

Visit us on the World Wide Web at: www.pearsonglobaleditions.com

© Pearson Education Limited 2016

Director of Operations: Nick Sklitsis

Operations Specialist: Maura Zaldivar-Garcia

$Senior\ Production\ Manufacturing\ Controller, Global\ Editions:$

Trudy Kimber

Media Production Manager, Global Editions: Vikram Kumar

Cover Art: © Shaparniy/Shutterstock

Manager, Rights and Permissions: Rachel Youdelman

Associate Project Manager, Rights and Permissions:

Timothy Nicholls Composition: Jouve India

The rights of Morris Mano, Charles R. Kime, and Tom Martin, to be identified as the authors of this work, have been asserted by them in accordance with the Copyright, Designs and Patents Act 1988.

Authorized adaptation from the United States edition, entitled Logic and Computer Design Fundamentals, ISBN 978-0-13-376063-7, by Morris Mano, Charles R. Kime, and Tom Martin, published by Pearson Education © 2016.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without either the prior written permission of the publisher or a license permitting restricted copying in the United Kingdom issued by the Copyright Licensing Agency Ltd, Saffron House, 6–10 Kirby Street, London EC1N 8TS.

Many of the designations by manufacturers and seller to distinguish their products are claimed as trademarks. Where those designations appear in this book, and the publisher was aware of a trademark claim, the designations have been printed in initial caps or all caps.

The author and publisher of this book have used their best efforts in preparing this book. These efforts include the development, research, and testing of theories and programs to determine their effectiveness. The author and publisher make no warranty of any kind, expressed or implied, with regard to these programs or the documentation contained in this book. The author and publisher shall not be liable in any event for incidental or consequential damages with, or arising out of, the furnishing, performance, or use of these programs.

Copyright © 2012 by Microsoft Corporation. Used with permission from Microsoft.

MICROSOFT AND/OR ITS RESPECTIVE SUPPLIERS MAKE NO REPRESENTATIONS ABOUT THE SUITABILITY OF THE INFORMATION CONTAINED IN THE DOCUMENTS AND RELATED GRAPHICS PUBLISHED AS PART OF THE SERVICES FOR ANY PURPOSE. ALL SUCH DOCUMENTS AND RELATED GRAPHICS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND. MICROSOFT AND/OR ITS RESPECTIVE SUPPLIERS HEREBY DISCLAIM ALLWARRANTIES AND CONDITIONS WITH REGARD TO THIS INFORMATION, INCLUDING ALLWARRANTIES AND CONDITIONS OF MERCHANTABILITY, WHETHER EXPRESS, IMPLIED OR STATUTORY, FITNESS FOR A PARTICULAR PURPOSE, TITLE AND NON-INFRINGEMENT. IN NO EVENT SHALL MICROSOFT AND/OR ITS RESPECTIVE SUPPLIERS BE LIABLE FOR ANY SPECIAL, INDIRECT OR CONSEQUENTIAL DAMAGES OR ANY DAMAGES WHATSOEVER RESULTING FROM LOSS OF USE, DATA OR PROFITS, WHETHER IN AN ACTION OF CONTRACT, NEGLIGENCE OR OTHER TORTIOUS ACTION, ARISING OUT OF OR IN CONNECTION WITH THE USE OR PERFORMANCE OF INFORMATION AVAILABLE FROM THE SERVICES. THE DOCUMENTS AND RELATED GRAPHICS CONTAINED HEREIN COULD INCLUDE TECHNICAL INACCURACIES OR TYPOGRAPHICAL ERRORS. CHANGES ARE PERIODICALLY ADDED TO THE INFORMATION HEREIN, MICROSOFT AND/OR ITS RESPECTIVE SUPPLIERS MAY MAKE IMPROVEMENTS AND/OR CHANGES IN THE PRODUCT(S) AND/OR THE PROGRAM(S) DESCRIBED HEREIN AT ANY TIME. PARTIAL SCREEN SHOTS MAY BE VIEWED IN FULL WITHIN THE SOFTWARE VERSION SPECIFIED.

### British Library Cataloguing-in-Publication Data

A catalogue record for this book is available from the British Library.

10987654321

ISBN 10: 1-292-09607-1 ISBN 13: 978-1-292-09607-0

Typeset by Jouve, in 10/12 Times Ten LT Std Printed and bound in Great Britain by Courier Westford

# Contents

| Preface  ☐ Chapter 1 | 19                                            | 12 |

|----------------------|-----------------------------------------------|----|

| DIGITAL SYST         | ems and Information                           | 19 |

| 1-1                  | Information Representation                    | 20 |

|                      | The Digital Computer                          | 22 |

|                      | Beyond the Computer                           | 23 |

|                      | More on the Generic Computer                  | 26 |

| 1-2                  | Abstraction Layers in Computer Systems Design | 28 |

|                      | An Overview of the Digital Design Process     | 30 |

| 1-3                  | Number Systems                                | 31 |

|                      | Binary Numbers                                | 33 |

|                      | Octal and Hexadecimal Numbers                 | 34 |

|                      | Number Ranges                                 | 36 |

| 1-4                  | Arithmetic Operations                         | 36 |

|                      | Conversion from Decimal to Other Bases        | 39 |

| 1-5                  | Decimal Codes                                 | 41 |

| 1-6                  | Alphanumeric Codes                            | 42 |

|                      | ASCII Character Code                          | 42 |

|                      | Parity Bit                                    | 45 |

| 1-7                  | Gray Codes                                    | 46 |

| 1-8                  | Chapter Summary                               | 48 |

|                      | References                                    | 49 |

|                      | Problems                                      | 49 |

| □ Chapter 2          | 53                                            |    |

| Combination          | al Logic Circuits                             | 53 |

| 2-1                  | Binary Logic and Gates                        | 54 |

|                      | Binary Logic Binary Logic                     | 54 |

|                      | Logic Gates                                   | 56 |

|                      | HDL Representations of Gates                  | 60 |

|                      | TIDE Representations of Gates                 | 00 |

| 4 | Contents |

|---|----------|

|   |          |

| 2-2          | Boolean Algebra                           | 61  |

|--------------|-------------------------------------------|-----|

| Z <b>-</b> Z | Basic Identities of Boolean Algebra       | 65  |

|              | Algebraic Manipulation                    | 67  |

|              | Complement of a Function                  | 70  |

| 2-3          | Standard Forms                            | 71  |

| 2 3          | Minterms and Maxterms                     | 71  |

|              | Sum of Products                           | 75  |

|              | Product of Sums                           | 76  |

| 2-4          | Two-Level Circuit Optimization            | 77  |

|              | Cost Criteria                             | 77  |

|              | Map Structures                            | 79  |

|              | Two-Variable Maps                         | 81  |

|              | Three-Variable Maps                       | 83  |

| 2-5          | Map Manipulation                          | 87  |

|              | Essential Prime Implicants                | 87  |

|              | Nonessential Prime Implicants             | 89  |

|              | Product-of-Sums Optimization              | 90  |

|              | Don't-Care Conditions                     | 91  |

| 2-6          | Exclusive-Or Operator and Gates           | 94  |

|              | Odd Function                              | 94  |

| 2-7          | Gate Propagation Delay                    | 96  |

| 2-8          | HDLs Overview                             | 98  |

|              | Logic Synthesis                           | 100 |

| 2-9          | HDL Representations—VHDL                  | 102 |

| 2-10         | HDL Representations – Verilog             | 110 |

| 2-11         | Chapter Summary                           | 117 |

|              | References                                | 118 |

|              | Problems                                  | 118 |

| □ Chapter    | 3 <b>129</b>                              |     |

| Combinatio   | ONAL LOGIC DESIGN                         | 129 |

| 3-1          | Beginning Hierarchical Design             | 130 |

| 3-2          | Technology Mapping                        | 134 |

| 3-3          | Combinational Functional Blocks           | 138 |

| 3-4          | Rudimentary Logic Functions               | 138 |

|              | Value-Fixing, Transferring, and Inverting | 139 |

|              | Multiple-Bit Functions                    | 139 |

|              | Enabling                                  | 142 |

| 3-5          | Decoding                                  | 144 |

|              | Decoder and Enabling Combinations         | 148 |

|              | Decoder-Based Combinational Circuits      | 151 |

| 3-6          | Encoding                                  | 153 |

|              | Priority Encoder                          | 154 |

|              | Encoder Expansion                         | 155 |

|             |                                          | Contents |   | 5          |

|-------------|------------------------------------------|----------|---|------------|

| 3-7         | Selecting                                |          | 1 | 56         |

|             | Multiplexers                             |          | 1 | 56         |

|             | Multiplexer-Based Combinational Circuits |          | 1 | 66         |

| 3-8         | Iterative Combinational Circuits         |          | 1 | 71         |

| 3-9         | Binary Adders                            |          | 1 | 73         |

|             | Half Adder                               |          | 1 | 73         |

|             | Full Adder                               |          |   | 74         |

|             | Binary Ripple Carry Adder                |          |   | 75         |

| 3-10        | Binary Subtraction                       |          |   | 77         |

|             | Complements                              |          |   | 78         |

|             | Subtraction Using 2s Complement          |          |   | 80         |

| 3-11        | Binary Adder-Subtractors                 |          |   | .81        |

|             | Signed Binary Numbers                    |          |   | .82        |

|             | Signed Binary Addition and Subtraction   |          |   | 84         |

|             | Overflow                                 |          |   | .86        |

|             | HDL Models of Adders                     |          |   | .88        |

| 2 12        | Behavioral Description                   |          |   | 90         |

| 3-12        | Other Arithmetic Functions               |          |   | 93         |

|             | Contraction                              |          |   | .94<br>.95 |

|             | Incrementing                             |          |   | 95         |

|             | Decrementing Multiplication by Constants |          |   | 96         |

|             | Division by Constants                    |          |   | 98         |

|             | Zero Fill and Extension                  |          |   | 98         |

| 3-13        | Chapter Summary                          |          |   | 99         |

| 3-13        | References                               |          |   | 99         |

|             | Problems                                 |          |   | 00         |

| □ Chapter 4 | 213                                      |          |   |            |

| SEQUENTIAL  |                                          |          | 2 | 13         |

| 4-1         | Sequential Circuit Definitions           |          |   | 14         |

| 4-2         | Latches                                  |          |   | 17         |

|             | $SR$ and $\overline{SR}$ Latches         |          |   | 217        |

|             | D Latch                                  |          |   | 20         |

| 4-3         | Flip-Flops                               |          |   | 20         |

|             | Edge-Triggered Flip-Flop                 |          |   | 22         |

|             | Standard Graphics Symbols                |          | 2 | 23         |

|             | Direct Inputs                            |          | 2 | 25         |

| 4-4         | Sequential Circuit Analysis              |          | 2 | 26         |

|             | Input Equations                          |          | 2 | 26         |

|             | State Table                              |          | 2 | 27         |

|             | State Diagram                            |          | 2 | 29         |

|             | Sequential Circuit Simulation            |          |   | 32         |

| 4-5         | Sequential Circuit Design                |          | 2 | 34         |

| 6 | Contents |

|---|----------|

|   |          |

|                 | Design Procedure                                     | 234 |

|-----------------|------------------------------------------------------|-----|

|                 | Finding State Diagrams and State Tables              | 235 |

|                 | State Assignment                                     | 242 |

|                 | Designing with D Flip-Flops                          | 243 |

|                 | Designing with Unused States                         | 246 |

|                 | Verification                                         | 248 |

| 4-6             | State-Machine Diagrams and Applications              | 250 |

|                 | State-Machine Diagram Model                          | 252 |

|                 | Constraints on Input Conditions                      | 254 |

|                 | Design Applications Using State-Machine Diagrams     | 256 |

| 4-7             | HDL Representation for Sequential Circuits—VHDL      | 264 |

| 4-8             | HDL Representation for Sequential Circuits – Verilog | 273 |

| 4-9             | Flip-Flop Timing                                     | 282 |

| 4-10            | Sequential Circuit Timing                            | 283 |

| 4-11            | Asynchronous Interactions                            | 286 |

| 4-12            | Synchronization and Metastability                    | 287 |

| 4-13            | Synchronous Circuit Pitfalls                         | 293 |

| 4-14            | Chapter Summary                                      | 294 |

|                 | References                                           | 295 |

|                 | Problems                                             | 296 |

| □ Chapter 5     | 311                                                  |     |

| DIGITAL HA      | rdware Implementation                                | 311 |

| 5-1             | The Design Space                                     | 311 |

|                 | Integrated Circuits                                  | 311 |

|                 | CMOS Circuit Technology                              | 312 |

|                 | Technology Parameters                                | 318 |

| 5-2             | Programmable Implementation Technologies             | 320 |

|                 | Read-Only Memory                                     | 322 |

|                 | Programmable Logic Array                             | 324 |

|                 | Programmable Array Logic Devices                     | 327 |

|                 | Field Programmable Gate Array                        | 329 |

| 5-3             | Chapter Summary                                      | 334 |

|                 | References                                           | 334 |

|                 | Problems                                             | 334 |

| □ Chapter 6     | 339                                                  |     |

| REGISTERS A     | nd Register Transfers                                | 339 |

| 6-1             | Registers and Load Enable                            | 340 |

| <b>U 1</b>      | Register with Parallel Load                          | 341 |

| 6-2             | Register Transfers                                   | 343 |

| 6-3             | Register Transfer Operations                         | 345 |

| 6-4             | Register Transfers in VHDL and Verilog               | 343 |

| U- <del>1</del> | register transfers in vitible and verning            | 34/ |

|             |                                           | Contents | 7                                 |

|-------------|-------------------------------------------|----------|-----------------------------------|

| 6-5         | Microoperations                           |          | 348                               |

|             | Arithmetic Microoperations                |          | 349                               |

|             | Logic Microoperations                     |          | 351                               |

|             | Shift Microoperations                     |          | 353                               |

| 6-6         | Microoperations on a Single Register      |          | 353                               |

|             | Multiplexer-Based Transfers               |          | 354                               |

|             | Shift Registers                           |          | 356                               |

|             | Ripple Counter                            |          | 361                               |

|             | Synchronous Binary Counters               |          | 363                               |

| 6.7         | Other Counters                            |          | 367                               |

| 6-7         | Register-Cell Design                      |          | 370                               |

| 6-8         | Multiple Registers                        |          | 275                               |

|             | Multiple Registers High-Impedance Outputs |          | <ul><li>375</li><li>377</li></ul> |

|             | Three-State Bus                           |          | 379                               |

| 6-9         | Serial Transfer and Microoperations       |          | 380                               |

| 0-7         | Serial Addition                           |          | 381                               |

| 6-10        | Control of Register Transfers             |          | 383                               |

| 0 10        | Design Procedure                          |          | 384                               |

| 6-11        | HDL Representation for Shift Registers    |          |                                   |

|             | and Counters—VHDL                         |          | 400                               |

| 6-12        | HDL Representation for Shift Registers    |          |                                   |

|             | and Counters—Verilog                      |          | 402                               |

| 6-13        | Microprogrammed Control                   |          | 404                               |

| 6-14        | Chapter Summary                           |          | 406                               |

|             | References                                |          | 407                               |

|             | Problems                                  |          | 407                               |

| □ Chapter 7 | 419                                       |          |                                   |

| MEMORY BAS  | ICS                                       |          | 419                               |

| 7-1         | Memory Definitions                        |          | 419                               |

| 7-2         | Random-Access Memory                      |          | 420                               |

|             | Write and Read Operations                 |          | 422                               |

|             | Timing Waveforms                          |          | 423                               |

|             | Properties of Memory                      |          | 425                               |

| 7-3         | SRAM Integrated Circuits                  |          | 425                               |

|             | Coincident Selection                      |          | 427                               |

| 7-4         | Array of SRAM ICs                         |          | 431                               |

| 7-5         | DRAM ICs                                  |          | 434                               |

|             | DRAM Cell                                 |          | 435                               |

|             | DRAM Bit Slice                            |          | 436                               |

| 7-6         | DRAM Types                                |          | 440                               |

|             | Synchronous DRAM (SDRAM)                  |          | 442                               |

|             | Double-Data-Rate SDRAM (DDR SDRAM)        |          | 444                               |

| _ |              |

|---|--------------|

| O | ~            |

| * | <br>Contents |

|   |              |

|             | RAMBUS® DRAM (RDRAM)             | 445 |

|-------------|----------------------------------|-----|

| 7-7         | Arrays of Dynamic RAM ICs        | 446 |

| 7-8         | Chapter Summary                  | 446 |

|             | References                       | 447 |

|             | Problems                         | 447 |

|             |                                  |     |

| □ Chapter 8 | 449                              |     |

| COMPUTER D  | esign Basics                     | 449 |

| 8-1         | Introduction                     | 450 |

| 8-2         | Datapaths                        | 450 |

| 8-3         | The Arithmetic/Logic Unit        | 453 |

|             | Arithmetic Circuit               | 453 |

|             | Logic Circuit                    | 456 |

|             | Arithmetic/Logic Unit            | 458 |

| 8-4         | The Shifter                      | 459 |

|             | Barrel Shifter                   | 460 |

| 8-5         | Datapath Representation          | 461 |

| 8-6         | The Control Word                 | 463 |

| 8-7         | A Simple Computer Architecture   | 469 |

|             | Instruction Set Architecture     | 469 |

|             | Storage Resources                | 470 |

|             | Instruction Formats              | 471 |

|             | Instruction Specifications       | 473 |

| 8-8         | Single-Cycle Hardwired Control   | 476 |

|             | Instruction Decoder              | 477 |

|             | Sample Instructions and Program  | 479 |

|             | Single-Cycle Computer Issues     | 482 |

| 8-9         | Multiple-Cycle Hardwired Control | 483 |

|             | Sequential Control Design        | 487 |

| 8-10        | Chapter Summary                  | 492 |

|             | References                       | 494 |

|             | Problems                         | 494 |

| □ Chapter 9 | 501                              |     |

| Instruction | Set Architecture                 | 501 |

| 9-1         | Computer Architecture Concepts   | 501 |

| · •         | Basic Computer Operation Cycle   | 503 |

|             | Register Set                     | 503 |

| 9-2         | Operand Addressing               | 504 |

| , 4         | Three-Address Instructions       | 505 |

|             | Two-Address Instructions         | 505 |

|             | One-Address Instructions         | 506 |

|             | One riddress monderations        | 300 |

|              | Zero-Address Instructions                                    | 506        |

|--------------|--------------------------------------------------------------|------------|

|              | Addressing Architectures                                     | 507        |

| 9-3          | Addressing Modes                                             | 510        |

|              | Implied Mode                                                 | 511        |

|              | Immediate Mode                                               | 511        |

|              | Register and Register-Indirect Modes                         | 512        |

|              | Direct Addressing Mode                                       | 512        |

|              | Indirect Addressing Mode                                     | 513        |

|              | Relative Addressing Mode                                     | 514        |

|              | Indexed Addressing Mode                                      | 515        |

|              | Summary of Addressing Modes                                  | 516        |

| 9-4          | Instruction Set Architectures                                | 517        |

| 9-5          | Data-Transfer Instructions                                   | 518        |

|              | Stack Instructions                                           | 518        |

|              | Independent versus Memory-Mapped I/O                         | 520        |

| 9-6          | Data-Manipulation Instructions                               | 521        |

|              | Arithmetic Instructions                                      | 521        |

|              | Logical and Bit-Manipulation Instructions                    | 522        |

| 0.7          | Shift Instructions                                           | 524        |

| 9-7          | Floating-Point Computations                                  | 525        |

|              | Arithmetic Operations                                        | 526        |

|              | Biased Exponent                                              | 527        |

| 0.0          | Standard Operand Format                                      | 528        |

| 9-8          | Program Control Instructions Conditional Branch Instructions | 530<br>531 |

|              | Procedure Call and Return Instructions                       | 533        |

| 9-9          |                                                              | 535        |

| 9-9          | Program Interrupts                                           | 536        |

|              | Types of Interrupts Processing External Interrupts           | 537        |

| 9-10         | Chapter Summary                                              | 538        |

| <i>y</i> -10 | References                                                   | 539        |

|              | Problems                                                     | 539        |

| □ Chapteı    | r 10 <b>547</b>                                              |            |

| RISC AND     | Cisc Central Processing Units                                | 547        |

| 10-1         | Pipelined Datapath                                           | 548        |

|              | Execution of Pipeline Microoperations                        | 552        |

| 10-2         | Pipelined Control                                            | 553        |

|              | Pipeline Programming and Performance                         | 555        |

| 10-3         | The Reduced Instruction Set Computer                         | 557        |

|              | Instruction Set Architecture                                 | 557        |

|              | Addressing Modes                                             | 560        |

|              | Datapath Organization                                        | 561        |

|              | Control Organization                                         | 564        |

Contents **9**

| 1 | Λ | _ | 0        |

|---|---|---|----------|

|   | v |   | Contents |

Data Hazards

|              | Control Hazards                        | 573 |

|--------------|----------------------------------------|-----|

| 10-4         | The Complex Instruction Set Computer   | 577 |

|              | ISA Modifications                      | 579 |

|              | Datapath Modifications                 | 580 |

|              | Control Unit Modifications             | 582 |

|              | Microprogrammed Control                | 583 |

|              | Microprograms for Complex Instructions | 585 |

| 10-5         | More on Design                         | 588 |

|              | Advanced CPU Concepts                  | 589 |

|              | Recent Architectural Innovations       | 592 |

| 10-6         | Chapter Summary                        | 595 |

|              | References                             | 596 |

|              | Problems                               | 597 |

| □ Chapter 11 | 601                                    |     |

| INPUT-OUTP   | ut and Communication                   | 601 |

| 11-1         | Computer I/O                           | 601 |

| 11-2         | Sample Peripherals                     | 602 |

|              | Keyboard                               | 602 |

|              | Hard Drive                             | 603 |

|              | Liquid Crystal Display Screen          | 605 |

|              | I/O Transfer Rates                     | 608 |

| 11-3         | I/O Interfaces                         | 608 |

|              | I/O Bus and Interface Unit             | 609 |

|              | Example of I/O Interface               | 610 |

|              | Strobing                               | 611 |

|              | Handshaking                            | 613 |

| 11-4         | Serial Communication                   | 614 |

|              | Synchronous Transmission               | 615 |

|              | The Keyboard Revisited                 | 616 |

|              | A Packet-Based Serial I/O Bus          | 617 |

| 11-5         | Modes of Transfer                      | 620 |

|              | Example of Program-Controlled Transfer | 621 |

|              | Interrupt-Initiated Transfer           | 622 |

| 11-6         | Priority Interrupt                     | 624 |

|              | Daisy Chain Priority                   | 624 |

|              | Parallel Priority Hardware             | 626 |

| 11-7         | Direct Memory Access                   | 627 |

|              | DMA Controller                         | 628 |

|              | DMA Transfer                           | 630 |

| 11-8         | Chapter Summary                        | 631 |

|              | References                             | 631 |

|              | Problems                               | 632 |

566

# □ Chapter 12 **635**

| Memory Systems |                              | 635 |

|----------------|------------------------------|-----|

| 12-1           | Memory Hierarchy             | 635 |

| 12-2           | Locality of Reference        | 638 |

| 12-3           | Cache Memory                 | 640 |

|                | Cache Mappings               | 642 |

|                | Line Size                    | 647 |

|                | Cache Loading                | 648 |

|                | Write Methods                | 649 |

|                | Integration of Concepts      | 650 |

|                | Instruction and Data Caches  | 652 |

|                | Multiple-Level Caches        | 653 |

| 12-4           | Virtual Memory               | 653 |

|                | Page Tables                  | 655 |

|                | Translation Lookaside Buffer | 657 |

|                | Virtual Memory and Cache     | 659 |

| 12-5           | Chapter Summary              | 659 |

|                | References                   | 660 |

|                | Problems                     | 660 |

| Index          |                              | 664 |

# **Preface**

The objective of this text is to serve as a cornerstone for the learning of logic design, digital system design, and computer design by a broad audience of readers. This fifth edition marks the continued evolution of the text contents. Beginning as an adaptation of a previous book by the first author in 1997, it continues to offer a unique combination of logic design and computer design principles with a strong hardware emphasis. Over the years, the text has followed industry trends by adding new material such as hardware description languages, removing or de-emphasizing material of declining importance, and revising material to track changes in computer technology and computer-aided design.

# **New to This Edition**

The fifth edition reflects changes in technology and design practice that require computer system designers to work at higher levels of abstraction and manage larger ranges of complexity than they have in the past. The level of abstraction at which logic, digital systems, and computers are designed has moved well beyond the level at which these topics are typically taught. The goal in updating the text is to more effectively bridge the gap between existing pedagogy and practice in the design of computer systems, particularly at the logic level. At the same time, the new edition maintains an organization that should permit instructors to tailor the degree of technology coverage to suit both electrical and computer engineering and computer science audiences. The primary changes to this edition include:

- Chapter 1 has been updated to include a discussion of the layers of abstractions in computing systems and their role in digital design, as well as an overview of the digital design process. Chapter 1 also has new material on alphanumeric codes for internationalization.

- The textbook introduces hardware description languages (HDLs) earlier, starting in Chapter 2. HDL descriptions of circuits are presented alongside logic schematics and state diagrams throughout the chapters on combinational and sequential logic design to indicate the growing importance of HDLs in contemporary digital system design practice. The material on propagation delay, which is a first-order design constraint in digital systems, has been moved into Chapter 2.

- Chapter 3 combines the functional block material from the old Chapter 3 and the arithmetic blocks from the old Chapter 4 to present a set of commonly

П

- occurring combinational logic functional blocks. HDL models of the functional blocks are presented throughout the chapter. Chapter 3 introduces the concept of hierarchical design.

- Sequential circuits appear in Chapter 4, which includes both the description of design processes from the old Chapter 5, and the material on sequential circuit timing, synchronization of inputs, and metastability from the old Chapter 6. The description of JK and T flip-flops has been removed from the textbook and moved to the online Companion Website.

- Chapter 5 describes topics related to the implementation of digital hardware, including design of complementary metal-oxide (CMOS) gates and programmable logic. In addition to much of the material from the old Chapter 6, Chapter 5 now includes a brief discussion of the effect of testing and verification on the cost of a design. Since many courses employing this text have lab exercises based upon field programmable gate arrays (FPGAs), the description of FPGAs has been expanded, using a simple, generic FPGA architecture to explain the basic programmable elements that appear in many commercially available FPGA families.

- The remaining chapters, which cover computer design, have been updated to reflect changes in the state-of-the art since the previous edition appeared. Notable changes include moving the material on high-impedance buffers from the old Chapter 2 to the bus transfer section of Chapter 6 and adding a discussion of how procedure call and return instructions can be used to implement function calls in high level languages in Chapter 9.

Offering integrated coverage of both digital and computer design, this edition of *Logic and Computer Design Fundamentals* features a strong emphasis on fundamentals underlying contemporary design. Understanding of the material is supported by clear explanations and a progressive development of examples ranging from simple combinational applications to a CISC architecture built upon a RISC core. A thorough coverage of traditional topics is combined with attention to computer-aided design, problem formulation, solution verification, and the building of problem-solving skills. Flexibility is provided for selective coverage of logic design, digital system design, and computer design topics, and for coverage of hardware description languages (none, VHDL, or Verilog®).

With these revisions, Chapters 1 through 4 of the book treat logic design, Chapters 5 through 7 deal with digital systems design, and Chapters 8 through 12 focus on computer design. This arrangement provides solid digital system design fundamentals while accomplishing a gradual, bottom-up development of fundamentals for use in top-down computer design in later chapters. Summaries of the topics covered in each chapter follow.

# **Logic Design**

**Chapter 1, Digital Systems and Information**, introduces digital computers, computer systems abstraction layers, embedded systems, and information representation including number systems, arithmetic, and codes.

**Chapter 2, Combinational Logic Circuits**, deals with gate circuits and their types and basic ideas for their design and cost optimization. Concepts include Boolean algebra, algebraic and Karnaugh-map optimization, propagation delay, and gate-level hardware description language models using structural and dataflow models in both VHDL and Verilog.

**Chapter 3, Combinational Logic Design**, begins with an overview of a contemporary logic design process. The details of steps of the design process including problem formulation, logic optimization, technology mapping to NAND and NOR gates, and verification are covered for combinational logic design examples. In addition, the chapter covers the functions and building blocks of combinational design including enabling and input-fixing, decoding, encoding, code conversion, selecting, distributing, addition, subtraction, incrementing, decrementing, filling, extension and shifting, and their implementations. The chapter includes VHDL and Verilog models for many of the logic blocks.

Chapter 4, Sequential Circuits, covers sequential circuit analysis and design. Latches and edge-triggered flip-flops are covered with emphasis on the D type. Emphasis is placed on state machine diagram and state table formulation. A complete design process for sequential circuits including specification, formulation, state assignment, flip-flop input and output equation determination, optimization, technology mapping, and verification is developed. A graphical state machine diagram model that represents sequential circuits too complex to model with a conventional state diagram is presented and illustrated by two real world examples. The chapter includes VHDL and Verilog descriptions of a flip-flop and a sequential circuit, introducing procedural behavioral VHDL and Verilog language constructs as well as test benches for verification. The chapter concludes by presenting delay and timing for sequential circuits, as well as synchronization of asynchronous inputs and metastability.

# **Digital Systems Design**

**Chapter 5, Digital Hardware Implementation**, presents topics focusing on various aspects of underlying technology including the MOS transistor and CMOS circuits, and programmable logic technologies. Programmable logic covers read-only memories, programmable logic arrays, programmable array logic, and field programmable gate arrays (FPGAs). The chapter includes examples using a simple FPGA architecture to illustrate many of the programmable elements that appear in more complex, commercially available FPGA hardware.

Chapter 6, Registers and Register Transfers, covers registers and their applications. Shift register and counter design are based on the combination of flip-flops with functions and implementations introduced in Chapters 3 and 4. Only the ripple counter is introduced as a totally new concept. Register transfers are considered for both parallel and serial designs and time–space trade-offs are discussed. A section focuses on register cell design for multifunction registers that perform multiple operations. A process for the integrated design of datapaths and control units using register transfer statements and state machine diagrams is introduced and illustrated by two real world examples. Verilog and VHDL descriptions of selected register types are introduced.

**Chapter 7, Memory Basics**, introduces static random access memory (SRAM) and dynamic random access memory (DRAM), and basic memory systems. It also describes briefly various distinct types of DRAMs.

# **Computer design**

**Chapter 8, Computer Design Basics**, covers register files, function units, datapaths, and two simple computers: a single-cycle computer and a multiple-cycle computer. The focus is on datapath and control unit design formulation concepts applied to implementing specified instructions and instruction sets in single-cycle and multiple-cycle designs.

**Chapter 9, Instruction Set Architecture**, introduces many facets of instruction set architecture. It deals with address count, addressing modes, architectures, and the types of instructions and presents floating-point number representation and operations. Program control architecture is presented including procedure calls and interrupts.

Chapter 10, RISC and CISC Processors, covers high-performance processor concepts including a pipelined RISC processor and a CISC processor. The CISC processor, by using microcoded hardware added to a modification of the RISC processor, permits execution of the CISC instruction set using the RISC pipeline, an approach used in contemporary CISC processors. Also, sections describe high-performance CPU concepts and architecture innovations including two examples of multiple CPU microprocessors.

**Chapter 11, Input–Output and Communication**, deals with data transfer between the CPU and memory, input–output interfaces and peripheral devices. Discussions of a keyboard, a Liquid Crystal Display (LCD) screen, and a hard drive as peripherals are included, and a keyboard interface is illustrated. Other topics range from serial communication, including the Universal Serial Bus (USB), to interrupt system implementation.

**Chapter 12, Memory Systems**, focuses on memory hierarchies. The concept of locality of reference is introduced and illustrated by consideration of the cache/main memory and main memory/hard drive relationships. An overview of cache design parameters is provided. The treatment of memory management focuses on paging and a translation lookaside buffer supporting virtual memory.

In addition to the text itself, a Companion Website and an Instructor's Manual are provided. Companion Website (www.pearsonglobaleditions.com/Mano) content includes the following: 1) reading supplements including material deleted from prior editions, 2) VHDL and Verilog source files for all examples, 3) links to computeraided design tools for FPGA design and HDL simulation, 4) solutions for about one-third of all text chapter problems, 5) errata, 6) PowerPoint® slides for Chapters 1 through 8, 7) projection originals for complex figures and tables from the text, and 8) site news sections for students and instructors pointing out new material, updates, and corrections. Instructors are encouraged to periodically check the instructor's site news so that they are aware of site changes. **Instructor's Manual** content includes suggestions for use of the book and all problem solutions. Online access to this manual is available from Pearson to instructors at academic institutions who adopt the

book for classroom use. The suggestions for use provide important detailed information for navigating the text to fit with various course syllabi.

Because of its broad coverage of both logic and computer design, this book serves several different objectives in sophomore through junior level courses. Chapters 1 through 9 with selected sections omitted, provide an overview of hardware for computer science, computer engineering, electrical engineering, or engineering students in general in a single semester course. Chapters 1 through 4 possibly with selected parts of 5 through 7 give a basic introduction to logic design, which can be completed in a single quarter for electrical and computer engineering students. Covering Chapters 1 through 7 in a semester provides a stronger, more contemporary logic design treatment. The entire book, covered in two quarters, provides the basics of logic and computer design for computer engineering and science students. Coverage of the entire book with appropriate supplementary material or a laboratory component can fill a two-semester sequence in logic design and computer architecture. Due to its moderately paced treatment of a wide range of topics, the book is ideal for self-study by engineers and computer scientists. Finally, all of these various objectives can also benefit from use of reading supplements provided on the Companion Website.

The authors would like to acknowledge the instructors whose input contributed to the previous edition of the text and whose influence is still apparent in the current edition, particularly Professor Bharat Bhuva, Vanderbilt University; Professor Donald Hung, San Jose State University; and Professors Katherine Compton, Mikko Lipasti, Kewal Saluja, and Leon Shohet, and Faculty Associate Michael Morrow, ECE, University of Wisconsin, Madison. We appreciate corrections to the previous editions provided by both instructors and students, most notably, those from Professor Douglas De Boer of Dordt College. In getting ready to prepare to think about getting started to commence planning to begin working on the fifth edition, I received valuable feedback on the fourth edition from Patrick Schaumont and Cameron Patterson at Virginia Tech, and Mark Smith at the Royal Institute of Technology (KTH) in Stockholm, Sweden. I also benefited from many discussions with Kristie Cooper and Jason Thweatt at Virginia Tech about using the fourth edition in the updated version of our department's Introduction to Computer Engineering course. I would also like to express my appreciation to the folks at Pearson for their hard work on this new edition. In particular, I would like to thank Andrew Gilfillan for choosing me to be the new third author and for his help in planning the new edition; Julie Bai for her deft handling of the transition after Andrew moved to another job, and for her guidance, support, and invaluable feedback on the manuscript; Pavithra Jayapaul for her help in text production and her patience in dealing with my delays (especially in writing this preface!); and Scott Disanno and Shylaja Gattupalli for their guidance and care in producing the text. Special thanks go to Morris Mano and Charles Kime for their efforts in writing the previous editions of this book. It is an honor and a privilege to have been chosen as their successor. Finally, I would like to thank Karen, Guthrie, and Eli for their patience and support while I was writing, especially for keeping our mutt Charley away from this laptop so that he didn't eat the keys like he did with its short-lived predecessor.

# GLOBAL EDITION

The publishers would like to thank the following for their contribution to the Global Edition:

# **Contributors**

Chiranjib Koley, Associate Professor, National Institute of Technology, Durgapur Lyla B. Das, Associate Professor, National Institute of Technology, Calicut

# **Reviewers**

Debaprasad Das, Professor, Assam University Moumita Mitra Manna, Lecturer of Computer Science and Applications at Bangabasi College, University of Calcutta Piyali Sengupta, Freelance

1

# DIGITAL SYSTEMS AND INFORMATION

his book deals with logic circuits and digital computers. Early computers were used for computations with discrete numeric elements called *digits* (the Latin word for fingers)—hence the term *digital computer*. The use of "digital" spread from the computer to logic circuits and other systems that use discrete elements of information, giving us the terms *digital circuits* and *digital systems*. The term *logic* is applied to circuits that operate on a set of just two elements with values True (1) and False (0). Since computers are based on logic circuits, they operate on patterns of elements from these two-valued sets, which are used to represent, among other things, the decimal digits. Today, the term "digital circuits" is viewed as synonymous with the term "logic circuits."

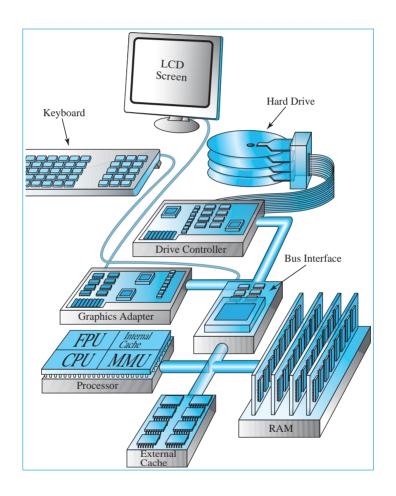

The general-purpose digital computer is a digital system that can follow a stored sequence of instructions, called a program, that operates on data. The user can specify and change the program or the data according to specific needs. As a result of this flexibility, general-purpose digital computers can perform a variety of informationprocessing tasks, ranging over a very wide spectrum of applications. This makes the digital computer a highly general and very flexible digital system. Also, due to its generality, complexity, and widespread use, the computer provides an ideal vehicle for learning the concepts, methods, and tools of digital system design. To this end, we use the exploded pictorial diagram of a computer of the class commonly referred to as a PC (personal computer) given on the opposite page. We employ this generic computer to highlight the significance of the material covered and its relationship to the overall system. A bit later in this chapter, we will discuss the various major components of the generic computer and see how they relate to a block diagram commonly used to represent a computer. We then describe the concept of layers of abstraction in digital system design, which enables us to manage the complexity of designing and programming computers constructed using billions of transistors. Otherwise, the remainder of the chapter focuses on the digital systems in our daily lives and introduces approaches for representing information in digital circuits and systems.

# 1-1 Information Representation

Digital systems store, move, and process information. The information represents a broad range of phenomena from the physical and man-made world. The physical world is characterized by parameters such as weight, temperature, pressure, velocity, flow, and sound intensity and frequency. Most physical parameters are *continuous*, typically capable of taking on all possible values over a defined range. In contrast, in the man-made world, parameters can be discrete in nature, such as business records using words, quantities, and currencies, taking on values from an alphabet, the integers, or units of currency, respectively. In general, information systems must be able to represent both continuous and discrete information. Suppose that temperature, which is continuous, is measured by a sensor and converted to an electrical voltage, which is likewise continuous. We refer to such a continuous voltage as an analog signal, which is one possible way to represent temperature. But, it is also possible to represent temperature by an electrical voltage that takes on discrete values that occupy only a finite number of values over a range, for example, corresponding to integer degrees centigrade between -40 and +119. We refer to such a voltage as a digital signal. Alternatively, we can represent the discrete values by multiple voltage signals, each taking on a discrete value. At the extreme, each signal can be viewed as having only two discrete values, with multiple signals representing a large number of discrete values. For example, each of the 160 values just mentioned for temperature can be represented by a particular combination of eight two-valued signals. The signals in most present-day electronic digital systems use just two discrete values and are therefore said to be binary. The two discrete values used are often called 0 and 1, the digits for the binary number system.

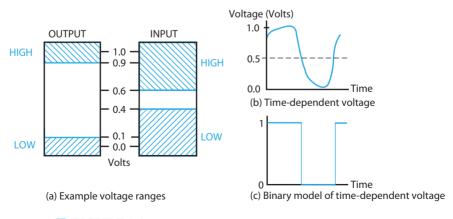

We typically represent the two discrete values by ranges of voltage values called HIGH and LOW. Output and input voltage ranges are illustrated in Figure 1-1(a). The HIGH output voltage value ranges between 0.9 and 1.1 volts, and the LOW output voltage value between -0.1 and 0.1 volts. The high input range allows 0.6 to 1.1 volts to be recognized as a HIGH, and the low input range allows

## ☐ FIGURE 1-1

Examples of Voltage Ranges and Waveforms for Binary Signals

-0.1 to 0.4 volts to be recognized as a LOW. The fact that the input ranges are wider than the output ranges allows the circuits to function correctly in spite of variations in their behavior and undesirable "noise" voltages that may be added to or subtracted from the outputs.

We give the output and input voltage ranges a number of different names. Among these are HIGH (H) and LOW (L), TRUE (T) and FALSE (F), and 1 and 0. It is natural to associate the higher voltage ranges with HIGH or H, and the lower voltage ranges with LOW or L. For TRUE and 1 and FALSE and 0, however, there is a choice. TRUE and 1 can be associated with either the higher or lower voltage range and FALSE and 0 with the other range. Unless otherwise indicated, we assume that TRUE and 1 are associated with the higher of the voltage ranges, H, and the FALSE and 0 are associated with the lower of the voltage ranges, L. This particular convention is called *positive logic*.

It is interesting to note that the values of voltages for a digital circuit in Figure 1-1(a) are still continuous, ranging from -0.1 to +1.1 volts. Thus, the voltage is actually analog! The actual voltages values for the output of a very high-speed digital circuit are plotted versus time in Figure 1-1(b). Such a plot is referred to as a waveform. The interpretation of the voltage as binary is based on a model using voltage ranges to represent discrete values 0 and 1 on the inputs and the outputs. The application of such a model, which redefines all voltage above 0.5 V as 1 and below 0.5 V as 0 in Figure 1-1(b), gives the waveform in Figure 1-1(c). The output has now been interpreted as binary, having only discrete values 1 and 0, with the actual voltage values removed. We note that digital circuits, made up of electronic devices called transistors, are designed to cause the outputs to occupy the two distinct output voltage ranges for 1 (H) and 0 (L) in Figure 1-1, whenever the outputs are not changing. In contrast, analog circuits are designed to have their outputs take on continuous values over their range, whether changing or not.

Since 0 and 1 are associated with the binary number system, they are the preferred names for the signal ranges. A binary digit is called a *bit*. Information is represented in digital computers by groups of bits. By using various coding techniques, groups of bits can be made to represent not only binary numbers, but also other groups of discrete symbols. Groups of bits, properly arranged, can even specify to the computer the program instructions to be executed and the data to be processed.

Why is binary used? In contrast to the situation in Figure 1-1, consider a system with 10 values representing the decimal digits. In such a system, the voltages available—say, 0 to 1.0 volts—could be divided into 10 ranges, each of length 0.1 volt. A circuit would provide an output voltage within each of these 10 ranges. An input of a circuit would need to determine in which of the 10 ranges an applied voltage lies. If we wish to allow for noise on the voltages, then output voltage might be permitted to range over less than 0.05 volt for a given digit representation, and boundaries between inputs could vary by less than 0.05 volt. This would require complex and costly electronic circuits, and the output still could be disturbed by small "noise" voltages or small variations in the circuits occurring during their manufacture or use. As a consequence, the use of such multivalued circuits is very limited. Instead, binary circuits are used in which correct circuit

operation can be achieved with significant variations in values of the two output voltages and the two input ranges. The resulting transistor circuit with an output that is either HIGH or LOW is simple, easy to design, and extremely reliable. In addition, this use of binary values makes the results calculated repeatable in the sense that the same set of input values to a calculation always gives exactly the same set of outputs. This is not necessarily the case for multivalued or analog circuits, in which noise voltages and small variations due to manufacture or circuit aging can cause results to differ at different times.

# **The Digital Computer**

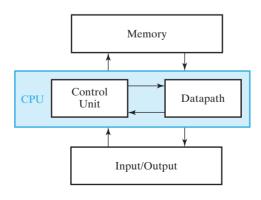

A block diagram of a digital computer is shown in Figure 1-2. The memory stores programs as well as input, output, and intermediate data. The datapath performs arithmetic and other data-processing operations as specified by the program. The control unit supervises the flow of information between the various units. A datapath, when combined with the control unit, forms a component referred to as a *central processing unit*, or CPU.

The program and data prepared by the user are transferred into memory by means of an input device such as a keyboard. An output device, such as an LCD (liquid crystal display), displays the results of the computations and presents them to the user. A digital computer can accommodate many different input and output devices, such as DVD drives, USB flash drives, scanners, and printers. These devices use digital logic circuits, but often include analog electronic circuits, optical sensors, LCDs, and electromechanical components.

The control unit in the CPU retrieves the instructions, one by one, from the program stored in the memory. For each instruction, the control unit manipulates the datapath to execute the operation specified by the instruction. Both program and data are stored in memory. A digital computer can perform arithmetic computations, manipulate strings of alphabetic characters, and be programmed to make decisions based on internal and external conditions.

☐ **FIGURE 1-2**Block Diagram of a Digital Computer

# **Beyond the Computer**

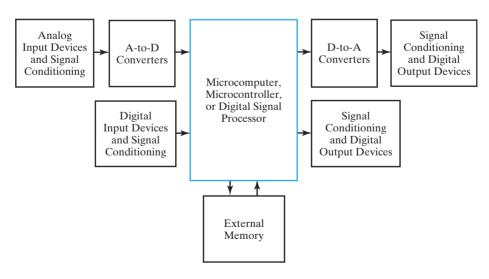

In terms of world impact, computers, such as the PC, are not the end of the story. Smaller, often less powerful, single-chip computers called microcomputers or microcontrollers, or special-purpose computers called digital signal processors (DSPs) actually are more prevalent in our lives. These computers are parts of everyday products and their presence is often not apparent. As a consequence of being integral parts of other products and often enclosed within them, they are called *embedded* systems. A generic block diagram of an embedded system is shown in Figure 1-3. Central to the system is the microcomputer (or its equivalent). It has many of the characteristics of the PC, but differs in the sense that its software programs are often permanently stored to provide only the functions required for the product. This software, which is critical to the operation of the product, is an integral part of the embedded system and referred to as embedded software. Also, the human interface of the microcomputer can be very limited or nonexistent. The larger informationstorage components such as a hard drive and compact disk or DVD drive frequently are not present. The microcomputer contains some memory; if additional memory is needed, it can be added externally.

With the exception of the external memory, the hardware connected to the embedded microcomputer in Figure 1-3 interfaces with the product and/or the outside world. The input devices transform inputs from the product or outside world into electrical signals, and the output devices transform electrical signals into outputs to the product or outside world. The input and output devices are of two types, those which use analog signals and those which use digital signals. Examples of digital input devices include a limit switch which is closed or open depending on whether a force is applied to it and a keypad having ten decimal integer buttons. Examples of

□ FIGURE 1-3

Block Diagram of an Embedded System

analog input devices include a thermistor which changes its electrical resistance in response to the temperature and a crystal which produces a charge (and a corresponding voltage) in response to the pressure applied. Typically, electrical or electronic circuitry is required to "condition" the signal so that it can be read by the embedded system. Examples of digital output devices include relays (switches that are opened or closed by applied voltages), a stepper motor that responds to applied voltage pulses, or an LED digital display. Examples of analog output devices include a loudspeaker and a panel meter with a dial. The dial position is controlled by the interaction of the magnetic fields of a permanent magnet and an electromagnet driven by the voltage applied to the meter.

Next, we illustrate embedded systems by considering a temperature measurement performed by using a wireless weather station. In addition, this example also illustrates analog and digital signals, including conversion between the signal types.

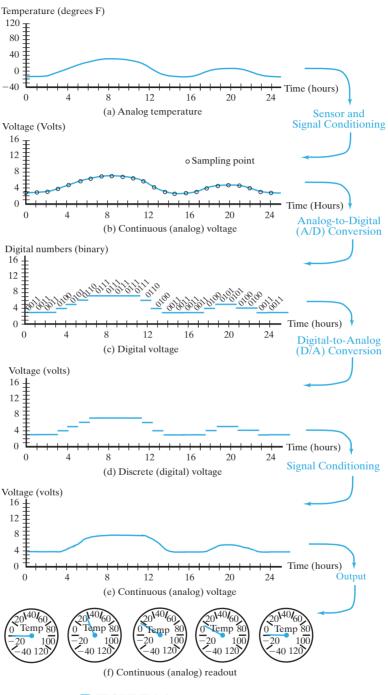

# **EXAMPLE 1-1** Temperature Measurement and Display

A wireless weather station measures a number of weather parameters at an outdoor site and transmits them for display to an indoor base station. Its operation can be illustrated by considering the temperature measurement illustrated in Figure 1-4 with reference to the block diagram in Figure 1-3. Two embedded microprocessors are used, one in the outdoor site and the other in the indoor base station.

The temperature at the outdoor site ranges continuously from  $-40^{\circ}\text{F}$  to  $+115^{\circ}\text{F}$ . Temperature values over one 24-hour period are plotted as a function of time in Figure 1-4(a). This temperature is measured by a sensor consisting of a thermistor (a resistance that varies with temperature) with a fixed current applied by an electronic circuit. This sensor provides an analog voltage that is proportional to the temperature. Using signal conditioning, this voltage is changed to a continuous voltage ranging between 0 and 15 volts, as shown in Figure 1-4(b).

The analog voltage is sampled at a rate of once per hour (a very slow sampling rate used just for illustration), as shown by the dots in Figure 1-4(b). Each value sampled is applied to an analog-to-digital (A/D) converter, as in Figure 1-3, which replaces the value with a digital number written in binary and having decimal values between 0 and 15, as shown in Figure 1-4(c). A binary number can be interpreted in decimal by multiplying the bits from left to right times the respective weights, 8, 4, 2, and 1, and adding the resulting values. For example, 0101 can be interpreted as  $0 \times 8 + 1 \times 4 + 0 \times 2 + 1 \times 1 = 5$ . In the process of conversion, the value of the temperature is quantized from an infinite number of values to just 16 values. Examining the correspondence between the temperature in Figure 1-4(a) and the voltage in Figure 1-4(b), we find that the typical digital value of temperature represents an actual temperature range up to 5 degrees above or below the digital value. For example, the analog temperature range between -25 and -15 degrees is represented by the digital temperature value of -20 degrees. This discrepancy between the actual temperature and the digital temperature is called the *quantization error*. In order to obtain greater precision, we would need to increase the number of bits beyond four in the output of the A/D converter. The hardware components for sensing, signal conditioning, and A/D conversion are shown in the upper left corner of Figure 1-3.

# ☐ FIGURE 1-4

Temperature Measurement and Display

Next, the digital value passes through the microcomputer to a wireless transmitter as a digital output device in the lower right corner of Figure 1-3. The digital value is transmitted to a wireless receiver, which is a digital input device in the base station. The digital value enters the microcomputer at the base station, where calculations may be performed to adjust its value based on thermistor properties. The resulting value is to be displayed with an analog meter shown in Figure 1-4(f) as the output device. In order to support this display, the digital value is converted to an analog value by a digital-to-analog converter, giving the quantized, discrete voltage levels shown in Figure 1-4(d). Signal conditioning, such as processing of the output by a low-pass analog filter, is applied to give the continuous signal in Figure 1-4(e). This signal is applied to the analog voltage display, which has been labeled with the corresponding temperature values shown for five selected points over the 24-hour period in Figure 1-4(f).

You might ask: "How many embedded systems are there in my current living environment?" Do you have a cell phone? An iPod<sup>TM</sup>? An Xbox<sup>TM</sup>? A digital camera? A microwave oven? An automobile? All of these are embedded systems. In fact, a late-model automobile can contain more than 50 microcontrollers, each controlling a distinct embedded system, such as the engine control unit (ECU), automatic braking system (ABS), and stability control unit (SCU). Further, a significant proportion of these embedded systems communicate with each other through a CAN (controller area network). A more recently developed automotive network, called FlexRay, provides high-speed, reliable communication for safety-critical tasks such as braking-by-wire and steering-by-wire, eliminating primary dependence on mechanical and hydraulic linkages and enhancing the potential for additional safety features such as collision avoidance. Table 1-1 lists examples of embedded systems classified by application area.

Considering the widespread use of personal computers and embedded systems, digital systems have a major impact on our lives, an impact that is not often fully appreciated. Digital systems play central roles in our medical diagnosis and treatment, in our educational institutions and workplaces, in moving from place to place, in our homes, in interacting with others, and in just having fun! The complexity of many of these systems requires considerable care at many levels of design abstraction to make the systems work. Thanks to the invention of the transistor and the integrated circuit and to the ingenuity and perseverance of millions of engineers and programmers, they indeed work and usually work well. In the remainder of this text, we take you on a journey that reveals how digital systems work and provide a detailed look at how to design digital systems and computers.

# More on the Generic Computer

At this point, we will briefly discuss the generic computer and relate its various parts to the block diagram in Figure 1-2. At the lower left of the diagram at the beginning of this chapter is the heart of the computer, an integrated circuit called the *processor*. Modern processors such as this one are quite complex and consist of tens to hundreds of millions of transistors. The processor contains four functional modules: the CPU, the FPU, the MMU, and the internal cache.

# □ TABLE 1-1 Embedded System Examples

| Application Area                    | Product                                                                                                                                |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Banking, commerce and manufacturing | Copiers, FAX machines, UPC scanners, vending machines, automatic teller machines, automated warehouses, industrial robots, 3D printers |

| Communication                       | Wireless access points, network routers, satellites                                                                                    |

| Games and toys                      | Video games, handheld games, talking stuffed toys                                                                                      |

| Home appliances                     | Digital alarm clocks, conventional and microwave ovens, dishwashers                                                                    |

| Media                               | CD players, DVD players, flat panel TVs, digital cameras, digital video cameras                                                        |

| Medical equipment                   | Pacemakers, incubators, magnetic resonance imaging                                                                                     |

| Personal                            | Digital watches, MP3 players, smart phones, wearable fitness trackers                                                                  |

| Transportation and navigation       | Electronic engine controls, traffic light controllers, aircraft flight controls, global positioning systems                            |

We have already discussed the CPU. The FPU (floating-point unit) is somewhat like the CPU, except that its datapath and control unit are specifically designed to perform floating-point operations. In essence, these operations process information represented in the form of scientific notation (e.g.,  $1.234 \times 10^7$ ), permitting the generic computer to handle very large and very small numbers. The CPU and the FPU, in relation to Figure 1-2, each contain a datapath and a control unit.

The MMU is the *memory management unit*. The MMU plus the internal cache and the separate blocks near the bottom of the computer labeled "External Cache" and "RAM" (*random-access memory*) are all part of the memory in Figure 1-2. The two caches are special kinds of memory that allow the CPU and FPU to get at the data to be processed much faster than with RAM alone. RAM is what is most commonly referred to as memory. As its main function, the MMU causes the memory that appears to be available to the CPU to be much, much larger than the actual size of the RAM. This is accomplished by data transfers between the RAM and the hard drive shown at the top of the drawing of the generic computer. So the hard drive, which we discuss later as an input/output device, conceptually appears as a part of both the memory and input/output.

The connection paths shown between the processor, memory, and external cache are the pathways between integrated circuits. These are typically implemented

as fine copper conductors on a printed circuit board. The connection paths below the bus interface are referred to as the processor bus. The connections above the bus interface are the input/output (I/O) bus. The processor bus and the I/O bus attached to the bus interface carry data having different numbers of bits and have different ways of controlling the movement of data. They may also operate at different speeds. The bus interface hardware handles these differences so that data can be communicated between the two buses.

All of the remaining structures in the generic computer are considered part of I/O in Figure 1-2. In terms of sheer physical volume, these structures dominate. In order to enter information into the computer, a keyboard is provided. In order to view output in the form of text or graphics, a graphics adapter card and LCD (*liquid crystal display*) screen are provided. The hard drive, discussed previously, is an electromechanical magnetic storage device. It stores large quantities of information in the form of magnetic flux on spinning disks coated with magnetic materials. In order to control the hard drive and transfer information to and from it, a drive controller is used. The keyboard, graphics adapter card, and drive controller card are all attached to the I/O bus. This allows these devices to communicate through the bus interface with the CPU and other circuitry connected to the processor buses.

# 1-2 Abstraction Layers in Computer Systems Design

As described by Moggridge, design is the process of understanding all the relevant constraints for a problem and arriving at a solution that balances those constraints. In computer systems, typical constraints include functionality, speed, cost, power, area, and reliability. At the time that this text is being written in 2014, leading edge integrated circuits have billions of transistors—designing such a circuit one transistor at a time is impractical. To manage that complexity, computer systems design is typically performed in a "top down" approach, where the system is specified at a high level and then the design is decomposed into successively smaller blocks until a block is simple enough that it can be implemented. These blocks are then connected together to make the full system. The generic computer described in the previous section is a good example of blocks connected together to make a full system. This book begins with smaller blocks and then moves toward putting them together into larger, more complex blocks.

A fundamental aspect of the computer systems design process is the concept of "layers of abstraction." Computer systems such as the generic computer can be viewed at several layers of abstraction from circuits to algorithms, with each higher layer of abstraction hiding the details and complexity of the layer below. Abstraction removes unnecessary implementation details about a component in the system so that a designer can focus on the aspects of the component that matter for the problem being solved. For example, when we write a computer program to add two variables and store the result in a third variable, we focus on the programming language constructs used to declare the variables and describe the addition operation. But when the program executes, what really happens is that electrical charge is moved around by transistors and stored in capacitive layers to represent the bits of data and

| Algorithms                   |  |  |

|------------------------------|--|--|

| Programming Languages        |  |  |

| Operating Systems            |  |  |

| Instruction Set Architecture |  |  |

| Microarchitecture            |  |  |

| Register Transfers           |  |  |

| Logic Gates                  |  |  |

| Transistor Circuits          |  |  |

### ☐ FIGURE 1-5

Typical Layers of Abstraction in Modern Computer Systems

control signals necessary to perform the addition and store the result. It would be difficult to write programs if we had to directly describe the flow of electricity for individual bits. Instead, the details of controlling them are managed by several layers of abstractions that transform the program into a series of more detailed representations that eventually control the flow of electrical charges that implement the computation.